据华中科技大学新闻网15日消息,该校材料成形与模具技术全国重点实验室教授翟天佑团队在二维高性能浮栅晶体管存储器方面取得重要进展,研制了一种具有边缘接触特征的新型二维浮栅晶体管器件,与现有商业闪存器件性能对比,其擦写速度、循环寿命等关键性能均有提升,为发展高性能、高密度大容量存储器件提供了新的思路。

浮栅晶体管作为一种电荷存储器,是构成当前大容量固态存储器发展的核心元器件。然而,当前,商业闪存内硅基浮栅存储器件所需的擦写时间约10μs-1ms范围,远低于计算单元CPU的数据处理速度(~ns) ,而其循环耐久性约为105次,也难以满足频繁的数据交互。随着计算机数据吞吐量的爆发式增长,突破传统浮栅晶体管擦写速度、耐久性等瓶颈,发展一种可兼顾高速、耐久特性的存储技术势在必行。

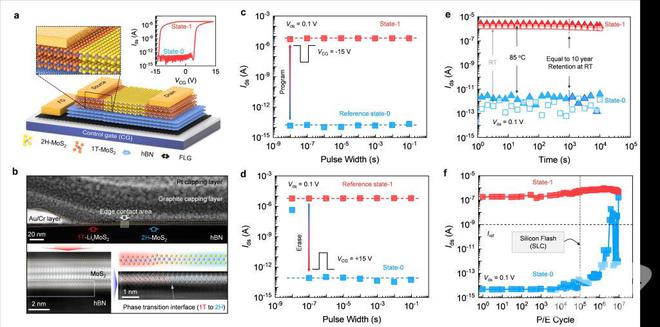

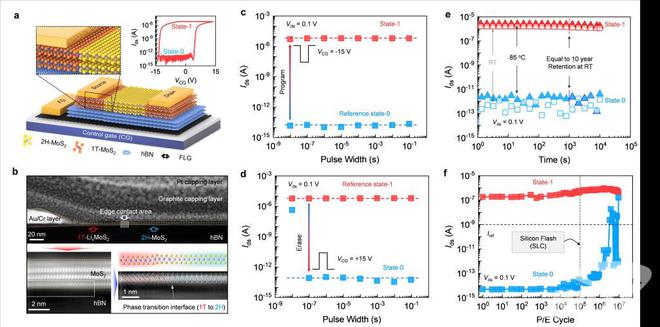

二维材料具有原子级厚度和无悬挂键表面,在器件集成时可有效避免窄沟道效应和界面态钉扎等问题,是实现高密度集成、高性能闪存器件的理想材料。然而,此前研究中,其数据擦写速度多异常缓慢,鲜有器件可同时实现高速和高循环耐久性。针对这一挑战,研究团队提出了一种具有边缘接触特征的新型二维浮栅晶体管器件,如图2所示,利用MoS2材料内独特的1T/2H金属-绝缘体相变工程在传统二维浮栅晶体管器件内引入边缘接触实现了擦写速度在10-100ns、循环耐久性超过3×106次的高性能存储器件。

研究中,团队利用化学Li+插层手段,对传统金属-半导体接触区域内MoS2进行相转变,使其由半导体相(2H)向金属相(1T)转变,使器件内金属-半导体接触类型由传统的3D/2D面接触过渡为具有原子级锐利界面的2D/2D型边缘接触。团队在长期的研究中发现,这种接触模式可有效避免接触势垒钉扎,从而有利于晶体管内通过金-半接触产生热电子注入,促进浮栅晶体管内电荷擦写效率的提升,在7-15V较低的工作电压和超短的脉冲下完成浮栅电荷的擦写,保证器件的循环耐久性。通过对比传统面接触电极与新型边缘接触,该研究说明了优化制备二维浮栅存储器件内金属-半导体接触界面对改善其擦写速度、循环寿命等关键性能的重要作用。

与现有商业闪存器件性能对比,研究所制备的二维浮栅晶体管在擦写速度、循环寿命方面均有了大幅度提升,展现出优越的存储性能。而作为一种适用于二维半导体器件的独特接触模式,新型边缘接触模式可有效避免接触电极尺寸效应,有利于接下来进一步推进其高密度集成,发展高性能、高密度大容量存储器件提供新的思路。

边缘接触式二维浮栅存储器的表征及其操作性能。

华中科技大学为该论文第一完成单位,材料学院博士研究生余军和硕士研究生王晗为论文共同第一作者,翟天佑教授、马颖教授和诸葛福伟副教授为通讯作者,集成电路学院缪向水教授和何毓辉教授等共同参与该项研究工作。本研究工作得到了国家自然科学基金(21825103、U21A2069)及科技部重点研发计划(2021YFA1200500)等项目的资助。